Rodrigo Bassi Guerreiro

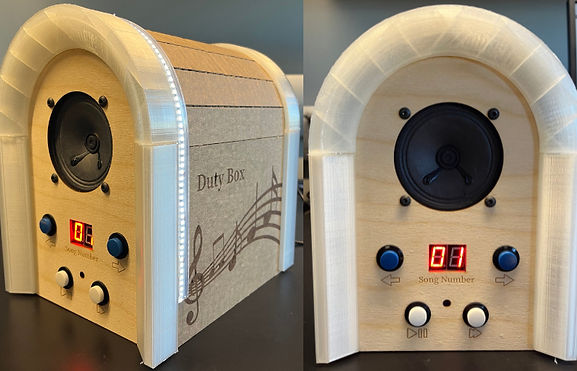

Duty Box

FPGA-based Jukebox

The Duty Box functions like a traditional jukebox would, allowing a user to choose a song to listen to out of a predetermined list. The most prominent feature of this project is that it is powered by a custom-made CPU core, implemented in an FPGA.

The project's name is a wordplay on the name of the jukebox, and the pulse-width modulation signals (defined by "duty cycles") that are sent out to this device's speaker.

Duration

November 2023 - December 2023

Team Size

2

Technologies

FPGA, Verilog, Xylinx Vivado, ESP32, 3D CAD

Technical Details

The processor core that supports the Duty Box was written entirely in gate-level Verilog, such that only modules external to the CPU used behavioral blocks. This RISC core had a 5-stage pipeline, and took in a subset of MIPS Assembly instructions. It also accepted a small set of custom instructions, mainly geared toward I/O in the final design. The Verilog designs were synthesized and implemented on the FPGA using Xylinx Vivado.

Due to memory constraints in the FPGA, an ESP32 Feather microcontroller with an embedded SD card slot was used to store the audio samples for the songs. It communicated with the FPGA using UART, along with other I/O pins to relax timing constraints.

As determined by the processor core, audio samples were requested to the microcontroller, and transferred into a circular buffer on the FPGA. One at a time, samples were taken from the buffer and scaled into the [0,100] range, which was interpreted as a duty cycle value. The PWM signal was then transmitted to the speaker, which had a built-in amplifier.

The physical assembly of the box was made out of laser-cut and engraved plywood frames for the front and back, a cardboard arch on the top and sides, and custom-made 3D-printed PLA pieces to connect them. This build allowed for the all the boards and wires to be neatly secured in place.

My Role

Aside from developing and testing the processor core, one of my main roles in this project was writing the Assembly code that would be run on that custom CPU. This included creating custom functions, carefully following calling conventions, and intertwining the internal logic with the external user inputs. It also allowed for the inclusion of additional features, like pausing and skipping songs, and even an "Easter Egg" from simultaneously pressing certain buttons.

Additionally, I handled most of the audio processing and transmitting. I experimented with different bit depths and sampling rates for the audio (analyzing the tradeoffs between transmission delay and audio quality), wrote the Verilog code to make the circular buffer, and used that logic to write the microcontroller code that would send the audio samples over UART on demand.

Video Demo

Showcase of all of the Duty Box's functionalities on demo day!